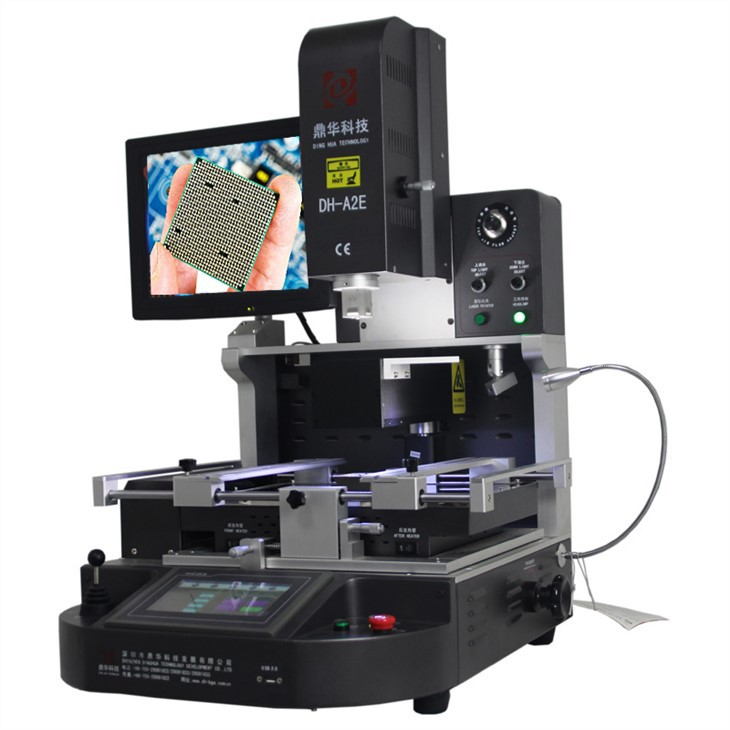

Ауто оптичка БГА станица за прераду

Широко се користи у поправци на нивоу чипа за матичне плоче мобилних, лаптопа, рачунара, ТВ-а, клима уређаја итд. Има високу успешну стопу поправке и висок степен аутоматизације и штеди много људских напора. Ми смо професионални произвођач ове машине и имамо ове машине на лагеру.

Opis

Ауто оптичка БГА станица за прераду

1. Примена Ауто Оптицал БГА Реворк Статион

Матична плоча рачунара, паметног телефона, лаптопа, МацБоок логичке плоче, дигиталне камере, клима уређаја, ТВ-а и друге електронике

опрема из медицинске индустрије, индустрије комуникација, аутомобилске индустрије итд.

Погодно за различите врсте чипова: БГА, ПГА, ПОП, БКФП, КФН, СОТ223, ПЛЦЦ, ТКФП, ТДФН, ТСОП, ПБГА, ЦПГА, ЛЕД чип.

2. Карактеристике производа аутоматске оптичке БГА станице за прераду

• Висока успешна стопа поправке на нивоу чипа. Процес одлемљења, монтаже и лемљења је аутоматски.

• Прецизно поравнање сваког лемног споја може се гарантовати са ЦЦД камером за оптичко поравнање.

•Прецизна контрола температуре може се обезбедити са 3 независна грејна подручја. Машина може да подеси и сачува

1 милион температурног профила.

• Уграђени вакуум у монтажној глави аутоматски преузима БГА чип након што је одлемљење завршено.

3.Спецификација аутоматске оптичке БГА станице за прераду

4.Детаљи аутоматске оптичке БГА станице за прераду

ЦЦД камера (прецизан оптички систем поравнања); 2.ХД дигитални дисплеј; 3. Микрометар (подешавање угла чипа);

4.3 независни грејачи (топли ваздух и инфрацрвени); 5. Ласерско позиционирање; 6. ХД интерфејс екрана осетљивог на додир, ПЛЦ контрола;

7.Лед хеадламп ; 8. Контрола џојстика .

5. Зашто одабрати нашу ауто оптичку БГА станицу за прераду?

6.Сертификат аутоматске оптичке БГА станице за прераду

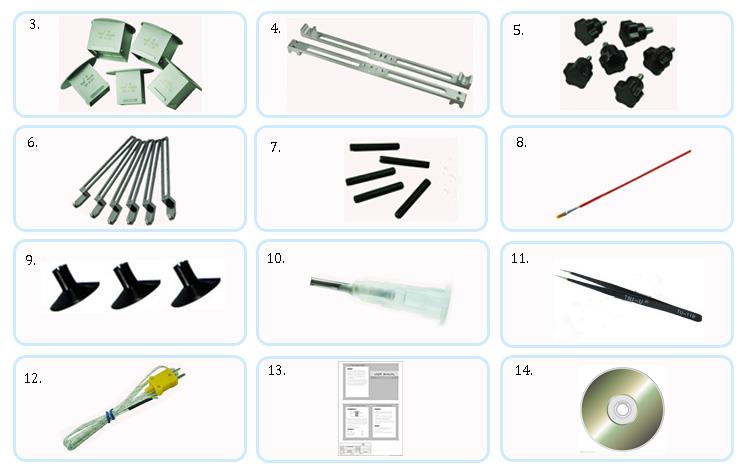

7. Паковање и испорука аутоматске оптичке БГА станице за прераду

8.ФАК

Како тестирати чип?

Почетни тест чипа на нивоу система

СоЦ је заснован на дубоким субмикронским процесима, тако да тестирање нових Соц уређаја захтева потпуно нови приступ. Јер свака функционална компонента

има своје захтеве за тестирање, инжењер пројекта мора да направи план тестирања у раној фази процеса пројектовања.

План тестирања блок по блок за СоЦ уређаје мора бити имплементиран: правилно конфигурисани АТПГ алати за тестирање логике; кратко време тестирања; нове велике брзине

модели грешака и тестови вишеструке меморије или малих низова. За производну линију, дијагностичка метода не само да проналази грешку, већ и раздваја

неисправан чвор из радног чвора. Поред тога, треба користити технике мултиплексирања тестова кад год је то могуће да би се уштедело време тестирања. У области високо

интегрисано ИЦ тестирање, АТПГ и ИДДК технике дизајна које се могу тестирати имају моћан механизам за раздвајање грешака.

Други стварни параметри које треба унапред планирати укључују број пинова које треба скенирати и количину меморије на сваком крају пинова.

Гранична скенирања могу бити уграђена у СоЦ, али нису ограничена на тестове међусобног повезивања на плочама или модулима са више чипова.

Иако се величина чипа смањује, чип и даље може да има милионе до 100 милиона транзистора, а број режима тестирања је порастао на невиђено

нивоа, што резултира дужим циклусима испитивања. Овај проблем се може тестирати. Режим компресије за решавање, однос компресије може да достигне 20 до 60 процената. За данашње велике

дизајн чипа, да би се избегли проблеми са капацитетом, неопходно је пронаћи софтвер за тестирање који може да ради на 64-битним оперативним системима.

Поред тога, тест софтвер се суочава са новим проблемима тестирања узрокованим дубоким субмикронским процесима и све већом учесталошћу. У прошлости је АТПГ режим тестирања за

тестирање грешака статичног блокирања више није било примењиво. Додавање функционалних образаца традиционалним алатима отежавало је проналажење нових грешака. Бољи приступ је да

класификовати групе претходних функционалних режима да би се утврдило које грешке не могу да се открију, а затим креирајте АТПГ режим за снимање ових недостајућих типова грешака.

Како се капацитет дизајна повећава и време тестирања по транзистору смањује, како би се пронашли проблеми повезани са брзином и проверили време кола, синхрони метод испитивања

мора бити запослен. Синхроно тестирање мора да укључује вишеструке моделе грешака, укључујући прелазне моделе, кашњења путање и ИДДК.

Неке компаније у индустрији верују да комбиновање грешака блокирања, функционалних и пролазних/кашњења путање може бити најефикаснија стратегија тестирања. За дубоко

субмикронски чипови и високофреквентни рад, тестирање пролазног стања и кашњења путање је још важније.

Да би се решио проблем АТЕ тачности при синхронизацији тестног језгра и смањио трошак, неопходно је пронаћи нови метод који поједностављује интерфејс

тест уређаја (тест прелазног стања и кашњења путање захтева тачан сат на интерфејсу уређаја за тестирање), Он обезбеђује да је сигнал довољно тачан током теста.

Пошто постоји велика могућност производних дефеката у СоЦ меморијском блоку, меморијски БИСТ мора имати дијагностичку функцију. Када се пронађе проблем,

дефектна адресна јединица се може мапирати у редундантну меморију резервне адресне јединице, а откривена адреса грешке ће бити одбачена. Избегавајте одбацивање

цео скупи чип.

Тестирање малих уграђених меморијских блокова елиминише потребу за додатним капијама или контролном логиком. На пример, технике тестирања векторске конверзије могу да конвертују

функционалне режиме у низ режима скенирања.

За разлику од БИСТ методе, функционални улаз заобилазног меморијског блока не захтева додатну логику. Пошто није потребна додатна логика тестирања, СоЦ

развојни инжењери могу поново да користе обрасце тестирања који су формирани у прошлости.

Напредни АТПГ алати не само да паралелно тестирају макрое, већ и одређују да ли постоје конфликти, као и детаљно који макрои могу да се тестирају паралелно, а који

макрои се не могу тестирати паралелно. Поред тога, ови макрои се могу ефикасно тестирати чак и ако је сат макроа исти као сат скенирања (као што је синхрона меморија).

Тренутно нема довољно тестних тачака на густој двостраној плочи, а сваки сложени чип мора бити опремљен граничним колом за скенирање. Без

скенирање граница, тражење грешака у производњи на нивоу плоче су прилично тешке и не могу се чак ни пронаћи. Са скенирањем граница, тестирање на нивоу плоче је изузетно лако

и независно од логичких кола унутар чипа. Гранично скенирање такође може да конфигурише АТПГ режим за ланац скенирања чипа у било којој фази производње.